Researchers at Harvard School of Engineering have observed that graphene electrons exhibit mass when they move together, although they are individually mass-less.

Professor Donhee Ham and Dr Hosang Yoon have successfully measured the collective mass of ‘massless’ electrons in motion in graphene.

By shedding light on the fundamental kinetic properties of electrons in graphene, this research may also provide a basis for the creation of circuits with graphene-based components.

“Graphene is a unique material because, effectively, individual graphene electrons act as though they have no mass. What that means is that the individual electrons always move at a constant velocity,” explains Ham. “But suppose we apply a force, like an electric field. The velocity of the individual electrons still remains constant, but collectively, they accelerate and their total energy increases—just like entities with mass. It’s quite interesting.”

Without this mass, the field of graphene plasmonics cannot work, so Ham’s team knew it had to be there—but until now, no one had accurately measured it.

“One of the greatest contributions of this work is that it is actually an extremely difficult measurement,” says Ham.

As Newton’s second law dictates, a force applied to a mass must generate acceleration. Yoon and Ham knew that if they could apply an electric field to a graphene sample and measure the electrons’ resulting collective acceleration, they could then use that data to calculate the collective mass.

But the graphene samples used in past experiments were replete with imperfections and impurities—places where a carbon atom was missing or had been replaced by something different. In those past experiments, electrons would accelerate but very quickly scatter as they collided with the impurities and imperfections.

“The scattering time was so short in those studies that you could never see the acceleration directly,” says Ham.

To overcome the scattering problem, several smart changes were necessary.

The team was able to reduce the number of impurities and imperfections by sandwiching the graphene between layers of hexagonal boron nitride, an insulating material with a similar atomic structure, and by designing a better way to connect electrical signal lines to the sandwiched graphene.

Yoon and Ham applied an electric field at a microwave frequency, which allows for the direct measurement of the electrons’ collective acceleration in the form of a phase delay in the current.

“By doing all this, we translated the situation from completely impossible to being at the verge of either seeing the acceleration or not,” says Ham. “However, the difficulty was still very daunting, and Hosang made it all possible by performing very fine and subtle microwave engineering and measurements—a formidable piece of experimentation.”

Collective mass is a key aspect of explaining plasmonic behaviors in graphene. By demonstrating that graphene electrons exhibit a collective mass and by measuring its value accurately, Yoon says, “We think it will help people to understand and design more sophisticated plasmonic devices with graphene.”

The challenge remains to improve the quality of graphene samples so that the detrimental effects of electron scattering can be further reduced.

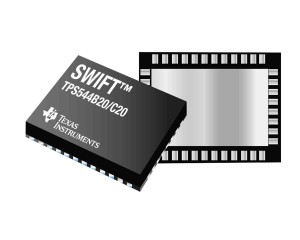

Texas Instruments has introduced its first 18V, 20A and 30A synchronous DC/DC buck converters with a PMBus digital power control interface.

Texas Instruments has introduced its first 18V, 20A and 30A synchronous DC/DC buck converters with a PMBus digital power control interface.