A team of Australian engineers has built a quantum logic gate in silicon for the first time, making calculations between two qubits of information possible. A crucial quantum computing hurdle has been overcome, according to the University of New South Wales (UNSW).

A team of Australian engineers has built a quantum logic gate in silicon for the first time, making calculations between two qubits of information possible. A crucial quantum computing hurdle has been overcome, according to the University of New South Wales (UNSW).

“High-fidelity two-qubit gates in the solid state that can be manufactured using standard lithographic techniques have so far been limited to superconducting qubits owing to the difficulties of coupling qubits and dephasing in semiconductor systems. Here we present a two-qubit logic gate, which uses single spins in isotopically enriched silicon and is realised by performing single and two-qubit operations in a quantum dot system using the exchange interaction,” said the UNSW team in a Nature abstract for the paper ‘A two-qubit logic gate in silicon‘.

The gate is a ‘controlled NOT’ (CNOT) gate.

A design for a quantum computer chip that would allow for millions of qubits has been patented, and industry partners are sought to make it.

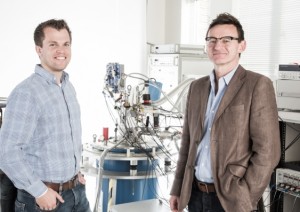

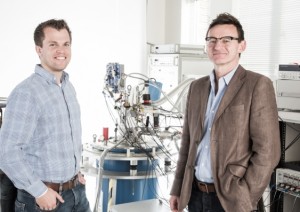

Menno Veldhorst (left in the photo) was lead author of the paper and Professor Andrew Dzurak (right) lead the project. Other UNSW contributors include Henry Yang and Andrea Morello – who leads the quantum spin control research team. Professor Kohei Itoh from Keio University in Japan provided special silicon wafers.

Quantum computers

In classical computers, data is rendered as binary bits, which are always in one of two states: 0 or 1.

A quantum bit (‘qubit’) can exist in both of these states at once – known as a superposition.

A qubit operation exploits this quantum weirdness by allowing many computations to be performed in parallel. According to UNSW, a two-qubit system performs the operation on four values, a three-qubit system on eight, and so on.

“If quantum computers are to become a reality, the ability to conduct one- and two-qubit calculations are essential,” said Dzurak, who jointly led the 2012 team that demonstrated the first ever silicon qubit, also reported in Nature.

In the gate, data is encoded as spin up or spin down – or the superposition of both.

Silicon electron spins have a usable coherence times’, after which data decays to randomness.

In 1998, according to the University, former UNSW researcher Bruce Kane first proposed the idea of using silicon as a base material for quantum computing. In Nature he outlined a silicon-based computer in which single phosphorus atoms in otherwise pure silicon define the qubits.

In 2012 Dzurak and Morello led a team that demonstrated a spin qubit in silicon, but in an atom rather than a transistor.

Last year Dzurak’s team discovered a way to create a qubit with a device similar to a mosfet.

Photo: Menno Veldhorst (left) and project leader Andrew Dzurak in the UNSW laboratory where the experiments were performed.

steve bush