Car manufacturers are adopting touch control technology in a big way. So much so that UK-based touch sensor firm Peratech has expanded resources in its North Yorkshire-based headquarters.

The company said it is seeing its QTC force touch sensors being integrated under in-car surfaces such as plastics, rubbers, wood, leather, metals and glass.

Neil Jarvie, Peratech sales v-p, says that the capability to incorporate pressure sensing that capacitive touch sensing does not provide is important for Tier 1 automotive companies.

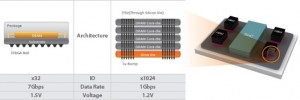

The matrix sensors are designed to track multiple touches for position on X and Y axes and independent pressure sensing along the Z-axis.

According to Jarvie, this allows designers to reduce button count in the centre stack, steering wheel and other cockpit surfaces.

“Replace the top surface of buttons with a display, and you have a Human Machine Interface (HMI) that is reconfigurable on the fly,” added Jarvie.

“Because the sensors aren’t affected by the electromagnetic interference of a display, we can make a display panel showing switches, sliders and knobs that actually work.”

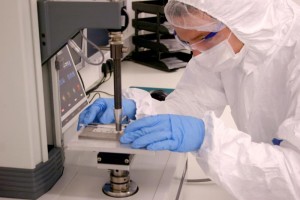

The firm’s sensors are tested for operation through cycles of -40 to +100 degrees C, which is the operational temperature range that the automotive industry requires.

“The requirement for a smart force touch display panel, first and foremost, is that is always works,” said Jarvie.